Описание

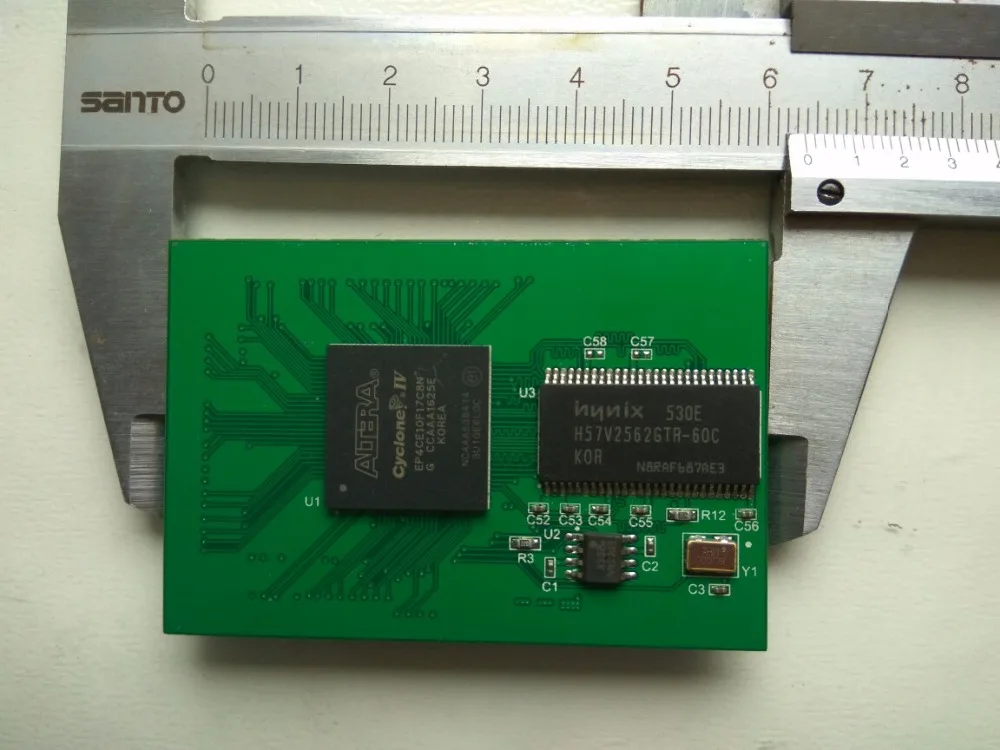

Аппаратные средства основной платы:

1. Ядро-это FPGA чип XC6SLX16-2FTG256.

2. Флэш-чип конфигурации W25Q64BV, 8 Мбайт пространства для хранения, а также может использоваться для хранения пользовательских данных.

3. Частицы памяти DDR3 MT41J64Mxx-15E, 1 Гбит (128 Мбайт) памяти, может поддерживать до 320 МГц основной частоты.

4. Поддержка JTAG и SPI режима конфигурации, в котором SPI может быть совместим с X1, X2, X4 режимом интерфейса.

5. Плата на активном кристаллическом осцилляторе 50 МГц, поддерживает пользователя для расширения часов.

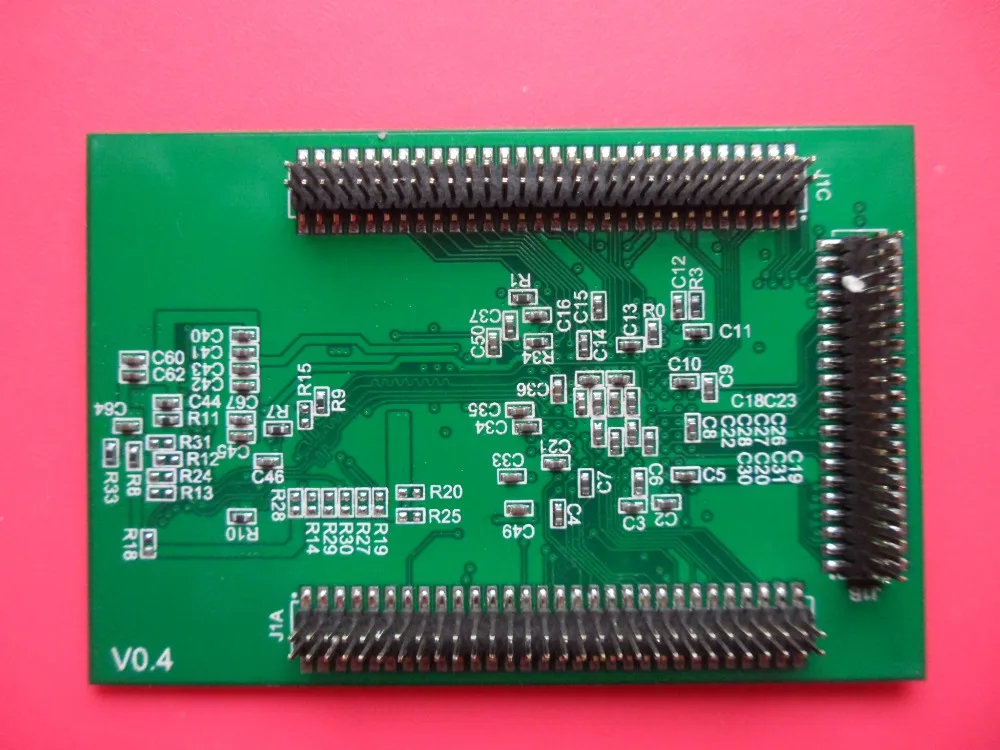

6. Остающиеся 120 IO Индуцированные Расширения могут образовывать 60 групп дифференциальных пар (LVDS).

7. Поддержка 12 комплектов LVDS тактового ввода/вывода.

8. Позолоченное основание расширения, 1,27 мм расстояние, подходит для двух разработок.

Экспериментальные процедуры основной платы включают:

1. Clk50M_div_1HZ, используя деление частоты счетчика

2. counter_8bit, 8bit гадюка

3. DDS_WaveGen, DDS генератор сигналов эксперимент

4. KEY_down_detect, обнаружение ключей, фильтрация и тряски

5. IO_test, IO тестовая программа

6. Мульт _ 4 бит, 4 бит мультипликатор эксперимент

7. ddr3_test, тест интерфейса DDR3

8. Сегмент _ шоу, эксперимент с цифровым дисплеем трубки

9. shifter_8bit, 8 bit shift register

Характеристики

- Бренд

- BETTERSHENGSUN

- Индивидуальное изготовление

- Да

- Test1

- 4

- Номер модели

- XC6SLX16

- Test4

- 4